2025年7月16日,第五届RISC-V中国峰会于上海举办。由中国科学院计算技术研究所联合哈尔滨工程大学、西华师范大学共同研发的RISC-V高性能编译器XSCC(XiangShang Compiler Collection)正式发布。这款面向香山"昆明湖"开源处理器架构优化的编译器,凭借卓越的性能优化效果与持续的开源贡献成为峰会焦点。

XSCC研发团队现场深度解析了编译器的设计理念、关键优化策略以及跨平台性能表现,吸引了众多业内专家驻足交流。多家企业现场表达了合作意向,希望将XSCC应用于更多实际场景中,进一步推动RISC-V生态系统的优化与发展。

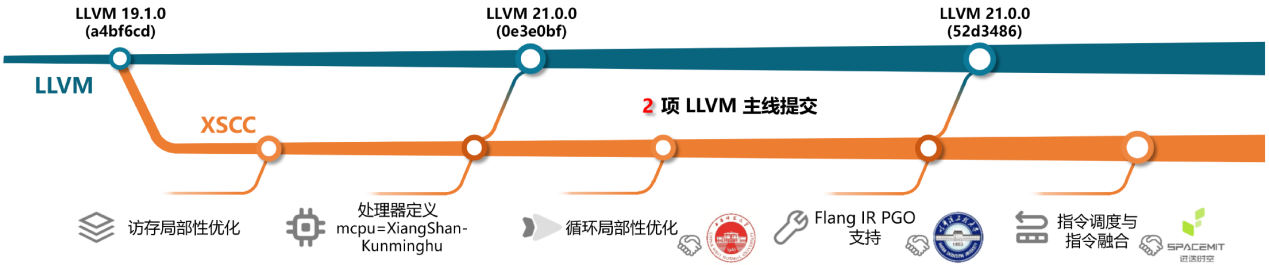

XSCC专为高性能RISC-V处理器设计,融合了访存优化、分支预测增强、循环变换与自动矢量化等多项关键优化技术,显著提升编译后代码的执行效率。测试数据显示:与LLVM 19.1.0相比,XSCC在speccpu2006基准测试中整型性能最高提升可达22%,浮点性能最高提升达20%。在适配进迭X60、阿里玄铁C920等其他主流RISC-V处理器平台时,XSCC亦展现出良好的通用性与可迁移性,定点性能最高提升达30%,浮点性能最高提升16%,充分体现出其强大的跨平台优化能力。同时联合研发团队长期致力于推动LLVM开源社区建设,目前已向主线贡献多项优化模块并成功合并,以实际行动支持开源编译器生态的发展。

哈尔滨工程大学作为XSCC编译器项目的战略支撑单位,由吴艳霞教授带领的嵌入式与体系结构创新团队深入参与多个关键优化模块的设计与实现,在整型与浮点型基准测试性能提升方面作出了突出贡献。在LLVM功能覆盖与Pass开发方面持续攻关,向LLVM社区贡献了多项自主研发成果,部分模块已成功并入LLVM主线仓库,彰显了我校在国际开源编译器领域的技术实力与持续投入。

多年来,嵌入式与体系结构团队与中国科学院计算技术研究所保持着紧密的合作关系,围绕编译器优化、高性能计算、处理器架构适配等方向开展了广泛而深入的联合研发。双方在多个科研项目中协同攻关,取得了一系列具有代表性的阶段性成果,为XSCC的发布打下了坚实基础。通过深度参与XSCC等前沿编译器项目,我院学子在RISC-V指令集优化、LLVM框架开发等核心技术领域获得实战锻炼,其开源贡献已获国际社区认可。这种产教融合的创新培养模式,既锻造了学生解决复杂工程问题的能力,更培育了开源协作的国际化视野。未来,将持续激励和引导更多青年才俊投身RISC-V工具链创新,为我国基础软件生态建设注入持续活力。